# Vector synthesis of fault testing map for logic

# Vladimir Hahanov<sup>1</sup>, Wajeb Gharibi<sup>2</sup>, Svetlana Chumachenko<sup>1</sup>, Eugenia Litvinova<sup>1</sup>

<sup>1</sup>Design Automation Department, Computer Engineering Faculty, Kharkiv National University of Radio Electronics, Kharkiv, Ukraine <sup>2</sup>Department of Computer Science and Electrical Engineering, University of Missouri, Kansas City, United States

#### **Article Info**

#### Article history:

Received Mar 2, 2024 Revised Jun 24, 2024 Accepted Jul 7, 2024

# Keywords:

Fault simulation mechanism

Fault testing map

Fault truth table

In-memory computing

Logic vector computing

Smart data structures

Test truth table

# **ABSTRACT**

Vector synthesis of fault testing (simulation) map for logic is proposed, which without simulation allows to determine of all faults detected on test sets, as well as determining test sets to detect specified faults. For synthesis, a superposition of smart data structures is used, containing: a deductive matrix D, as a derivative of the logical vector L, test truth table T, and fault truth table F. The deductive matrix is seen as the gene of functionality and base of fault simulation mechanism to solve all the problems of testing and verification. In the matrix synthesis, an axiom is used: all the mentioned tables are identical in shape to each other and always interact with each other convolutionally T\(\phi\L\phi\F=0\). A universal deductive reversing converter "test-faults" and "faults-test" for logical functionalities of any dimension is proposed. Converter functions: fault simulation on test sets T

F and synthesis of test sets  $F \rightarrow T$  to detect the specified faults. The converter can be used as a test generation and fault simulation service for IP-core systemon-chip (SoC) under the IEEE 1500 SECT standard. Based on the deductive matrix, a fault testing map for logic is built, where each test set is matched with the logic-detected faults of the input lines.

This is an open access article under the <u>CC BY-SA</u> license.

293

# Corresponding Author:

Vladimir Hahanov

Design Automation Department, Computer Engineering Faculty, Kharkiv National University of Radio

Electronics Kharkiv, Ukraine

Email: hahanov@icloud.com

#### 1. INTRODUCTION

System-on-chip (SoC) IP-core testing is dealt with by thousands of specialists and hundreds of companies that find reasonable technological and software solutions to create a product yield in a reasonable time-to-market [1]–[4]. At the same time, companies should pay more attention to mathematics and data structures, which could be better in almost most industrial systems for designing and testing digital devices. The market design metric "quick solution is better than correct one" leads any system with hundreds of software and hardware patches to a state inoperable for the market over a long time [1], [5]–[7]. The way out: the development of mathematically smart, as a rule, long-lived data structures invariant to the rapid change in programming technologies and the element base of digital systems [1], [8]–[10]. On such well-thought-out data structures, very compact, simple algorithms for their analysis are obtained [1], [3], [11]–[14]. There is a design pattern: if you spend 90% of your time on the mathematical culture of smart data structures, the time for creating simple algorithms for their processing will not be more than 10% [13], [15]–[20].

The Intelligent Computing Technology Metric [21]–[30] offers the following time and energy saving solutions. First is read-write transactions on memory [16]–[21], [26]. Second is in-memory synthesis of a simple logical processor [10], [11], [28]. Third is using RISC-V architecture instructions to process data in memory [21], [24], [31]. Fourth is synthesis of smart data structures for information processing without an

Journal homepage: http://ijra.iaescore.com

algorithm [22], [23], [27], [29]. Finally, it is Neumann architecture in-memory to control data processing [21], [25], [30].

In-memory computing is gradually capturing new areas of the information technology (IT) industry due to the absence of iterations between memory and the central processor, which significantly saves energy in the intelligent processing of big data [21]–[30]. In addition, redundancy memory has reached the processor's logical command speed [21], [24], [26], [30], forcing companies to leverage memory services to organize computing processes. Many publications consider memory as a convenient tool for implementing big data processing algorithms on a limited set of instructions for deterministic and probabilistic computing, including machine learning and artificial neural networks [22]–[25], [27], [28]. In addition, only in-memory read-write transactions can be leveraged to build big data processing architectures free from processor instructions [16]–[21]. The synthesis of smart data structures makes it possible to code computational algorithms based on in-memory read-write transactions [1], [16]–[19], [30] with a speed of 1 ns or less.

Statement of the fault simulation problem. Fault simulation is essential for Automatic Test Pattern Generation (ATPG) [3]–[5], [10]–[13], diagnosis [10]–[12], [16], [17], and fault and test grading [16], [17], [32]–[35]. Fault simulation metrics are speed, memory, modeling functional blocks and delay capability, sequential circuits, multi-valued fault simulation to handle unknown X, and high-impedance Z [16], [17], [32]–[35]. In addition to the circuit model, a fault simulator usually needs stimuli and expected responses (required for true-value simulation), a fault model, and a fault list. Concurrent fault simulation [33], [34] is an event-driven simulation that involves good/bad events together. The simulated part of faulty circuits differs from that of good circuits. Memory management is complex. Practically all industrial fault simulation systems have unpredictable sizes of fault lists and unpredictable sizes of data structures. All six primary simulation engines use a processor with a high-power consumption level. The Electronic Design Automation (EDA) market needs simple and efficient fault simulation mechanisms to verify tests [1], [18], [19]. A metric comparison of fault simulation mechanisms existing in industrial systems is given in Table 1. Vector fault simulation is also evaluated in this metric, for which all metric points, except for one here, are in black.

Table 1. Fault simulation techniques: metrics comparison

|                      |                                             |               | 1                 |        |             |         |       |           |

|----------------------|---------------------------------------------|---------------|-------------------|--------|-------------|---------|-------|-----------|

| Fault simulation     | Complexity                                  | Memory        | Data structure    | Level  | Delay       | Speed   | Fault | Multi-    |

| technique            |                                             | •             |                   |        | •           | -       | model | valued    |

| Serial fault         | $n \times n^3$                              | Predictable   | Add fault         | Gate,  | No problem  | Slowest | Any   | Easy      |

| simulation [34]      |                                             |               | model, fault list | system |             |         |       |           |

| Parallel fault       | $\frac{1}{w} \times n^3$                    | Predictable   | Register          | Gate   | Not capable | Middle  | Logic | Difficult |

| simulation [3]       | W                                           |               | Memory            |        |             |         |       |           |

| Deductive fault      | $n^2$                                       | Unpredictable | Deductive         | Gate   | Not capable | Middle  | Any   | Difficult |

| simulation [32]      |                                             | •             | formulas          |        | •           |         | •     |           |

| Concurrent fault     | $\frac{1}{3} \times n^2$                    | Unpredictable | Add fault         | Gate,  | Capable     | Faster  | Logic | Easy      |

| simulation [33]      | 3                                           | _             | model, fault list | RTL    | _           |         | _     | -         |

| PPSFP - Parallel     | $\frac{1}{w} \times n^3$                    | Unpredictable | Add fault         | Gate   | Capable     | Middle  | Logic | Easy      |

| pattern single fault | w                                           |               | model, fault list |        |             |         |       |           |

| propagation [10]     |                                             |               |                   |        |             |         |       |           |

| Differential fault   | $\frac{1}{2} \times n^2$                    | Unpredictable | Add fault         | Gate,  | Not capable | Middle  | Any   | Difficult |

| simulation [35]      | 2                                           | _             | model, fault list | RTL    | _           |         | -     |           |

| Vector fault         | $\frac{1}{2} \times \frac{1}{3} \times n^2$ | Predictable   | No, as true-      | Gate,  | Not capable | Faster  | Logic | Capable   |

| simulation [18]      | 2 3                                         |               | value simulation  | RTL,   | _           |         | _     | _         |

|                      |                                             |               |                   | System |             |         |       |           |

The goal is to significantly reduce the latency and energy consumption of in-memory computing for fault simulation of Boolean functionality by modeling a deductive matrix via smart data structures on a logic vector. The objective of this paper is to i) develop smart (connected) data structures based on a logical vector, including a deductive matrix and two truth tables: tests and faults, ii) development of an algorithm for simulation faults on a test set, iii) create of an algorithm for generating test sets for given faults, iv) synthesis of a reversible converter of test sets into detected faults and vice versa, detected faults into test sets, v) synthesis of fault testing map for logic using a deductive matrix, and vi) verification of data structures and algorithms for their analysis.

A new scientific direction of vector logical computing (VLC) is proposed. This is processor-free computation in memory based on read-write transactions on logical vectors. The new vector logic computing metrics for fault modeling and simulation are i) free-from-processor data processing means energy-saving computing technology, ii) the absence of the classical von Neumann architecture means no iterations between the data bus between memory and the arithmetic logic unit (ALU), significantly reducing data processing time, iii) read-write transactions instead of a robust processor instruction set that allows you to organize the

computational process on any memory device, iv) logical vectors assume their simple placement in memory without time-consuming synthesis into a technologically permitted system of elements, v) an address is an attribute of memory and truth tables and a fault as address simulation mechanism, vi) smart data structures reduce the algorithm for their analysis to linear computational complexity, vii) all digital functionality testing tasks are solved using a logical vector and its derivatives, and viii) the simulation of tests and faults on the truth table addresses does not include the simulation algorithm. Everything set out in the metric of vector-logical computing, as well as models, methods, algorithms, and mechanisms for fault as address simulation, is new and has no global analogs. The advantage of the proposed study is that it reduces models and algorithms to simple engineering mechanisms.

# 2. DEDUCTIVE MATRIX SYNTHESIS

The truth table is an ideal model for solving all combinatorial problems, including test synthesis and fault simulation [17]. The logical vector is the most compact universal model of a logical element. D-matrix is a genome for solving all problems in the field of design and testing. These three models comprise smart data structures for organizing any in-memory testing SoC IP-core. The properties of the deductive matrix obtained from the logical vector for solving the problems of synthesis and analysis of the test by simulation faults are considered. Smart data structures make it possible to solve the problem of transporting input faults to the output without simulation when a binary set is put to the inputs of a logic element. The problem of synthesis of a minimum test for input faults of a component is also solved by trivial analysis of the deductive matrix. The essence of these methods is to build smart data structures based on a logical vector (truth table), by interacting the logical vector "with itself," a quadratic matrix of the activity of the logical element is built. Recoding the coordinates of this matrix by binary-decimal addresses leads to a deductive matrix, which initially solves the problems of test generation and fault simulation efficiently. The computational complexity of solving these problems is determined by a quadratic estimate of the length of the logical vector  $C=2^n \times 2^n$ . To create a deductive matrix, follow five steps of the algorithm as shown in Figure 1.

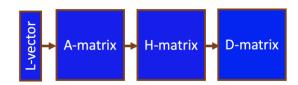

Figure 1. Algorithm for creating deductive matrix

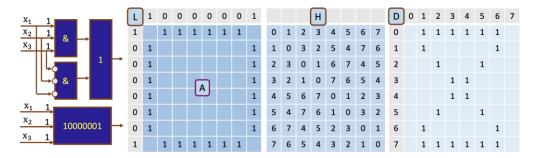

- i. Initial data: the logical L-vector of functionality from n-variables is written horizontally and vertically in the active A-matrix in Figure 2.

- iii. The activity matrix A, consisting of logical vectors and their inversions, is created based on the given logical vector. Construction of A-activity table rows as shown in Figure 2 carried out according to the rule:  $A_i = L \oplus L_i$ . Here  $Q_i$ , the state of the i-bit of the logical (vertical) L-vector. Put, if the coordinate of the vertical L-vector is equal to 1, then the inversion of the logical vector  $A_i = \overline{L}$  is written to the corresponding row of the A-matrix. Otherwise, the logical vector  $A_i = L$  is written to the row. Empty cells in the matrices denote zero coordinates to reduce the load on vision. The activity A-matrix is always symmetrical in relation to the main diagonal. A deductive matrix is an active matrix, bits of which are ordered by binary-decimal addresses via an H-matrix.

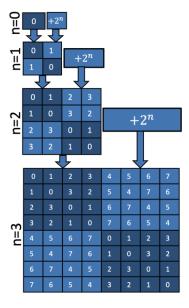

- iii. The bit-recoding matrix H is needed to build a deductive matrix quickly. The H-matrix is the same for all logical functionalities from n variables. The recursive mechanism of H-matrix synthesis in Figure 3 uses the operations sequentially to calculate the coordinates of the four quadrants: 1)  $H_{i+1}^1 = H_i$ ; 2)  $H_{i+1}^2 = 2^n + H_i$ ; 3)  $H_{i+1}^3 = H_{i+1}^2$ ;  $H_{i+1}^4 = H_{i+1}^1$ .

iv. Creating of deductive D-matrix by the formula:  $D_j = L_{H_{ij}}$ ,  $j = \overline{1, 2^n}$ , which recodes the bits of the A-activity matrix according to the H-matrix recoding coordinates addresses (obtained in step 3 of the algorithm). Thus, the D-matrix is obtained based on the execution of the operator  $D = (L \oplus L_i)_H$ , obtained because of the superposition of the operators:  $A = L \oplus L_i$  and  $D = A_H$ . D-matrix is a genome for solving all problems in the field of design and testing.

v. A synthesis of a logical functionality testing map is carried out using a deductive matrix. Section 5 of this paper will describe this procedure.

Figure 2. Procedure for creating a deductive matrix

Figure 3. Recursive scheme for obtaining H-matrix of recoding

# 3. ANALYSIS OF DEDUCTIVE MATRICES

It is straightforward to create deductive matrices of logical functionalities in n-variables. However, it remains to clarify the deductive matrix's beneficial properties for solving fault simulation problems and testing the generation of logical functionalities. Deductive matrices of three essential elements from three variables have the form in Figure 4.

The first helpful property of the deductive matrix is that without simulation, it determines all input faults detected on the test set. Simulation formula: Based on the binary test set, a row of the D-matrix is selected, the 1-unit values of which activate the 1-unit coordinates of the upper fault TT, which are additionally determined by the inverse values of the coordinates of the selected column of the truth table equal to the test set. Following the simulation formula, we determine which faults are detected on test set 101 of all three elements. The first matrix gives the following result: stuck-at-1 is detected on the second input  $X_2=1$ . The second matrix forms the result of the multiple fault check:  $X_1, X_3=0$ . The third matrix forms the following checked stuck-at-faults:  $X_1=0, X_2=1, X_3=0$ , multiple fault  $X_1, X_2, X_3=0$ 10. Thus, the

deductive matrix without simulation detects faults of any combination on the binary input set, which are described by 1-unit coordinates in the columns of the fault TT. All interacting components, such as tests, faults, and logic, are defined on the same truth table (logical vector), the derivative of which is the deductive matrix.

| X <sub>1</sub> | X <sub>2</sub> | <b>X</b> <sub>3</sub> |   |                 |                 | (L=0             | 00000           | 001)             |                  |                   | <b>X</b> <sub>1</sub> | $X_2$  | <b>X</b> <sub>3</sub> |                 | D               | (L=0:            | 11111           | 11)              |                  |                   | <b>X</b> <sub>1</sub> | <b>X</b> <sub>2</sub> | <b>X</b> <sub>3</sub> |                 | D              | (L=01            | 11010           | 01)              |                  |   |

|----------------|----------------|-----------------------|---|-----------------|-----------------|------------------|-----------------|------------------|------------------|-------------------|-----------------------|--------|-----------------------|-----------------|-----------------|------------------|-----------------|------------------|------------------|-------------------|-----------------------|-----------------------|-----------------------|-----------------|----------------|------------------|-----------------|------------------|------------------|---|

|                |                | X <sub>1</sub>        |   |                 |                 |                  |                 |                  |                  |                   |                       |        | X <sub>1</sub>        |                 |                 |                  |                 |                  |                  |                   |                       |                       | X <sub>1</sub>        |                 |                |                  |                 |                  |                  |   |

|                |                | X <sub>2</sub>        |   |                 |                 |                  |                 |                  |                  |                   |                       |        | X <sub>2</sub>        |                 |                 |                  |                 |                  |                  |                   |                       |                       | X <sub>2</sub>        |                 |                |                  |                 |                  |                  |   |

|                |                | X <sub>3</sub>        |   |                 |                 |                  |                 |                  |                  |                   |                       |        | X <sub>3</sub>        |                 |                 |                  |                 |                  |                  |                   |                       |                       | Х3                    |                 |                |                  |                 |                  |                  |   |

|                | 0              |                       |   |                 |                 |                  |                 |                  |                  | 1                 | 0                     |        |                       | 1               | 1               |                  | 1               |                  |                  | 1                 | 0                     |                       |                       | 1               |                |                  | 1               |                  |                  |   |

| 1              | 0              |                       |   |                 |                 |                  |                 |                  | 1                |                   | 1                     |        |                       | 1               |                 |                  |                 |                  |                  |                   | 1                     |                       |                       | 1               | 1              |                  | 1               |                  |                  | 1 |

| 0              | 1              |                       |   |                 |                 |                  |                 | 1                |                  |                   | 0                     |        |                       |                 | 1               |                  |                 |                  |                  |                   | 0                     |                       |                       | 1               |                |                  | 1               |                  |                  |   |

| 1              | 1              |                       |   |                 |                 |                  | 1               |                  |                  |                   | 1                     |        |                       |                 |                 | 1                |                 |                  |                  |                   | 1                     |                       |                       | 1               | 1              |                  | 1               |                  |                  | 1 |

|                | 0              |                       |   |                 |                 | 1                |                 |                  |                  |                   | 0                     |        |                       |                 |                 |                  | 1               |                  |                  |                   | 0                     |                       |                       | 1               |                |                  | 1               |                  |                  |   |

| 1              | 0              |                       |   |                 | 1               |                  |                 |                  |                  |                   | 1                     |        |                       |                 |                 |                  |                 | 1                |                  |                   | 1                     |                       |                       | 1               |                |                  | 1               |                  |                  |   |

| 0              | 1              |                       |   | 1               |                 |                  |                 |                  |                  |                   | 0                     |        |                       |                 |                 |                  |                 |                  | 1                |                   | 0                     |                       |                       | 1               | 1              |                  | 1               |                  |                  | 1 |

| 1              | 1              |                       | 0 | 1               | 1               | 1                | 1               | 1                | 1                | 1                 | 1                     |        |                       |                 |                 |                  |                 |                  |                  | 1                 | 1                     |                       |                       | 1               | 1              |                  | 1               |                  |                  | 1 |

| De             | rivativ        | /es →                 |   | X' <sub>1</sub> | X' <sub>2</sub> | X' <sub>12</sub> | X' <sub>3</sub> | X' <sub>13</sub> | X' <sub>23</sub> | X' <sub>123</sub> | Dei                   | ivativ | es →                  | X' <sub>1</sub> | X' <sub>2</sub> | X' <sub>12</sub> | X' <sub>3</sub> | X' <sub>13</sub> | X' <sub>23</sub> | X' <sub>123</sub> | Der                   | ivativ                |                       | X' <sub>1</sub> | X <sub>2</sub> | X' <sub>12</sub> | X' <sub>3</sub> | X' <sub>13</sub> | X' <sub>23</sub> |   |

Figure 4. Deductive matrices of three basic logical functions

#### 4. DEDUCTIVE REVERSIBLE CONVERTER

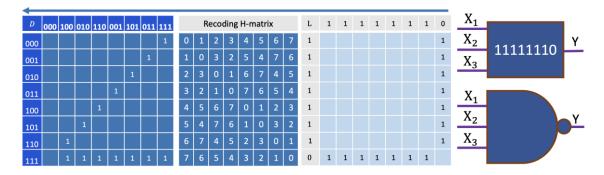

Next, a deductive reversible converter is proposed that, without simulation, allows you to determine all the faults detected on test sets (define test sets for detected given faults), thanks to the superposition of smart data structures in memory [17], including two truth tables: test TT, faults TT and deductive D-matrix. Figure 5 shows an example of the synthesis of a deductive matrix and its leverage for fault simulation and test generation on the same data structures. Empty cells in the active and deductive matrix and faults TT indicate zero coordinates.

Figure 5. Synthesis of the deductive matrix of a logical element

Using the deductive matrix, one can quickly generate a test for stuck-at-faults of the input variables (columns 1, 2, 4), which has the form of T = (110, 111, 101, 111, 011, 111) = (110, 101, 011, 111). The test is obtained by projecting each column (1, 2, 4) with faults to all 1-unit coordinates of the D-matrix, the projection of which onto the test TT rows form the minimum test. Geometrically, the algorithm is represented by the angle " $\downarrow$ " of two arrows that define test sets by the deductive matrix:  $\downarrow$  – from each chosen column of faults TT, descend to the intersection with the matrix 1-units,  $\leftarrow$  – then from the matrix 1-units we move to the left until the intersection with the rows of the test TT.

As for the simulation of faults for the L=011111111 element: let us have 4 test sets: 110, 101, 011, 111. When simulating manually, we will carry out such a " $\rightarrow$ 1" movement along the matrix from the test set to the right until it intersects with 1-units and then up from them to the intersection with the columns of faults TT, where each 1-unit of the column is converted into a fault, the sign of which is determined by the inversion of the state of the input variable on the test set. The results of the simulation of faults on test sets are as follows:  $110 - X_1 = 1$ ,  $101 - X_2 = 1$ ,  $011 - X_1 = 1$ , 111:  $X_1 = 0$ ,  $X_2 = 0$ ,  $X_3 = 0$ , and all their four possible combinations.

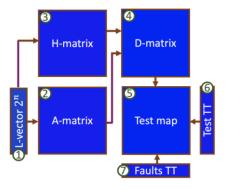

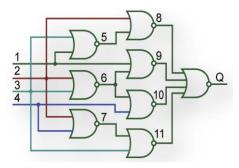

An innovative solution to design and test problems is practically proposed as a universal deductive reversible converter "test faults" and "faults  $\rightarrow$  test" based on the deductive matrix in Figure 6 for logical functionalities of any dimension. The functions of the converter are i) fault simulation on test sets F=D(T) and ii) generating test sets that detect given faults T=D(F). On the converter, it is possible to perform fault diagnosis of logical devices on given test sets and verify the test to detect a given set of faults in a logic element in percent.

Figure 6. Deductive reversable test–fault converter and his two functions

To create such a converter from three smart (connected) components, it is necessary to generate the rows A-activity matrix leveraging the coordinate-vector operation  $A_i = L \bigoplus L_i$  based on the logical L-vector and transform it into a deductive D-matrix using the recoding matrix of coordinates addresses  $D = A_H$  as shown in Figure 7. The recoding matrix is the universal key for obtaining the deductive matrix of any n-input element. The deductive matrix is a genome for solving all the problems of testing digital functional elements of any complexity. The formula for obtaining the D-matrix is  $D = (L \bigoplus L_i)_H$ .

Figure 7. Scheme for obtaining a deductive matrix

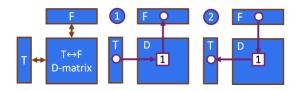

The fee for creating such services is a sufficiently large memory required to store the deductive matrix and two truth tables  $M = 2^n \times 2^n + 2 \times 2^n$ , n - the number of input variables of the functional logic element. If we talk about the entire fault simulation mechanism (FSM) in Figure 8, then its implementation also requires memory for the synthesis of the deductive matrix:  $M = 2 \times (2^n \times 2^n) + 2^n$ . The memory estimation for data storage (logical vector, two truth tables, and three quadratic matrices) to implement the entire FSM is  $M = 3(2^n \times 2^n) + 2^n + 2n \times 2^n$ .

Figure 8. The structure of the fault simulation mechanism

Let us talk about the novelty of the research. Smart data structures based on the logical L-vector of the element are described here, which allows the creation of a deductive matrix (blocks 1 to 4) and leverage it

as a reverse in-memory converter for fault simulation and test synthesis (blocks 4 to 6) based on truth tables: Test TT, Faults TT and deductive D-matrices, which form a common topological space used to describe FSM. This mechanism contains four procedures for sequentially creating four matrices based on a logical L-vector: A-matrix – H-matrix – D-matrix – S-matrix (simulation). The last matrix is also called the fault testing map (FT-map). In this scheme, the essence of the mechanism for fault simulation of logical elements of any dimension. It could not be easier.

The formula of D-matrix synthesis [17], as presented in Figure 8, are as follows. According to the logical L-vector of functionality (block 1) a quadratic A-matrix of activity (block 2) is created, where each row is a logical vector or its or its inversion  $A_i$ =  $L \oplus L_i$  depending on the state of the i-cell of the L-vector and, then all the coordinates of the resulting A-matrix are ordered by the indices of the quadratic recoding H-matrix (block 3) to obtain a deductive D-matrix (block 4 and 5), which is a reverse converter of the test set into detected faults and vice versa, where the 1-unit values of the D-matrix coordinate define a one-to-one correspondence between the rows (test sets) of test TT (block 6) and columns (combination of faults) faults TT (block 7). Formula for fault simulation: from the selected test set, move to the right along the term of the deductive matrix until it intersects with 1-coordinate, then move up from each 1-unit until it intersects with the columns of faults TT, where the inverse states of the input variables of the test set further define the 1-unit coordinates. Formula for test synthesis: from selected in faults TT of the column as combinations of faults specified by 1-units, the movement is carried out down the deductive matrix until it meets the 1-units of the D-matrix, after which it moves from 1-units to the left until it meets the test sets of Test TT, which always detect combinations of faults that are inverse to the states of the variables on the test set.

The technological novelty of the fault simulation mechanism lies in placing all components of smart data structures (6 components) in any memory that can be processed by a limited set of logical commands in the limit read—write transactions. The synthesis and operation of the converter do not require a powerful system of CPU instructions, which makes it economical in terms of energy and time for fault simulation (test generation) since a read-write transaction on emergence memory is completed in 1 ns.

#### 5. SYNTHESIS FAULT TESTING MAP

The goal is to move from a deductive matrix to an explicit assignment of all faults to be detected on test input sets. To do this, it is necessary to define all 1-coordinates of the deductive matrix with fault vectors detected on the test set by constructing a projection of the 1-coordinate of the matrix onto the vectors of the test and fault truth tables. In other words, it is necessary to record the faults detected on the test set in the 1-coordinates of the deductive matrix. To do this, superpositions of two truth tables are performed: tests and faults based on a deductive matrix.

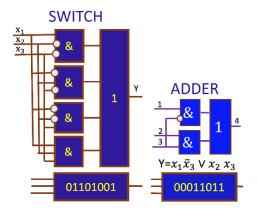

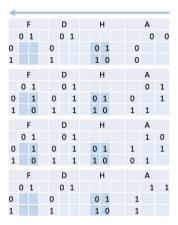

The examples of processing logical functionalities as shown in Figure 9 are switch circuits and adder circuits. These circuits have a known structure, but only a logical vector synthesizes the test-fault converter. Obtaining a fault testing map for these two functionalities is accompanied by three operations presented from left to right in Figure 10: i) obtaining an activity matrix by manipulating a logical vector, ii) synthesizing a deductive matrix based on applying bit transcoding matrix activity to the matrix, and iii) constructing a test-fault map by superposition of test sets with fault table codes at 1-values of the coordinates of the deductive matrix.

Figure 9. Logic circuits considered as elements

| <b>—</b> |     |     |     |      |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |     |     |     |       |   |   |   |   |     |   |   |     |       |      |     |   |   |

|----------|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|---|---|---|---|-----|---|---|-----|-------|------|-----|---|---|

|          |     |     | Te  | st-m | ар  |     |     |     |     |     |     | D-  | -mat | rix |     |     |     |     |     |     | H-  | -ma | atrix | ĸ |   |   |   |     |   |   | Log | gic v | vect | tor |   |   |

| TT       | 000 | 001 | 010 | 011  | 100 | 101 | 110 | 111 | TT  | 000 | 001 | 010 | 011  | 100 | 101 | 110 | 111 |     |     |     |     |     |       |   |   |   | - | L   | 0 | 1 | 1   | 0     | 1    | 0   | 0 | 1 |

| 000      |     | 1   | .1. |      | 1   |     |     | 111 | 000 |     | 1   | 1   |      | 1   |     |     | 1   | (   | ) : | 1   | 2   | 3   | 4     | 5 | 6 | 7 | ( | )   |   | 1 | 1   |       | 1    |     |   | 1 |

| 001      |     | 0   | .1. |      | 1   |     |     | 110 | 001 |     | 1   | 1   |      | 1   |     |     | 1   |     | L ( | 0 : | 3   | 2   | 5     | 4 | 7 | 6 | : | l   | 1 |   |     | 1     |      | 1   | 1 |   |

| 010      |     | 1   | .0. |      | 1   |     |     | 101 | 010 |     | 1   | 1   |      | 1   |     |     | 1   | - : | 2 3 | 3   | 0   | 1   | 6     | 7 | 4 | 5 | : | l   | 1 |   |     | 1     |      | 1   | 1 |   |

| 011      |     | 0   | .0. |      | 1   |     |     | 100 | 011 |     | 1   | 1   |      | 1   |     |     | 1   | 3   | 3 2 | 2   | 1   | 0   | 7     | 6 | 5 | 4 | ( | )   |   | 1 | 1   |       | 1    |     |   | 1 |

| 100      |     | 1   | .1. |      | 0   |     |     | 011 | 100 |     | 1   | 1   |      | 1   |     |     | 1   | 4   | 1 ! | 5   | 6   | 7   | 0     | 1 | 2 | 3 | : | l   | 1 |   |     | 1     |      | 1   | 1 |   |

| 101      |     | 0   | .1. |      | 0   |     |     | 010 | 101 |     | 1   | 1   |      | 1   |     |     | 1   |     | 5 4 | 4   | 7   | 6   | 1     | 0 | 3 | 2 | ( | )   |   | 1 | 1   |       | 1    |     |   | 1 |

| 110      |     | 1   | .0. |      | 0   |     |     | 001 | 110 |     | 1   | 1   |      | 1   |     |     | 1   | (   | 5 7 | 7 . | 4   | 5   | 2     | 3 | 0 | 1 | ( | )   |   | 1 | 1   |       | 1    |     |   | 1 |

| 111      |     | 0   | .0. |      | 0   |     |     | 000 | 111 |     | 1   | 1   |      | 1   |     |     | 1   |     | 7 ( | 6   | 5   | 4   | 3     | 2 | 1 | 0 | : | 1   | 1 |   |     | 1     |      | 1   | 1 |   |

| •        |     |     |     |      |     |     |     |     |     |     |     |     |      |     |     |     |     |     |     |     |     |     |       |   |   |   |   |     |   |   |     |       |      |     |   |   |

|          |     |     | Tes | st-m | ар  |     |     |     |     |     |     | T-  | matı | rix |     |     |     |     |     |     | F-  | ma  | trix  | < |   |   |   |     |   |   | Ŀ   | -ma   | atri | K   |   |   |

| П        | 000 | 001 | 010 | 011  | 100 | 101 | 110 | 111 | П   | 000 | 001 | 010 | 011  | 100 | 101 | 110 | 111 |     |     |     |     |     |       |   |   |   | ١ | ( ( | 0 | 0 | 0   | 1     | 1    | 0   | 1 | 1 |

| 000      |     |     |     | .11  | 1   |     | 11. | 111 | 000 |     |     |     | 1    | 1   |     | 1   | 1   | (   | ) 1 | L 2 | 2   | 3   | 4     | 5 | 6 | 7 | ( | )   |   |   |     | 1     | 1    |     | 1 | 1 |

| 001      |     |     | .1. |      |     | 1.0 | 11. | 110 | 001 |     |     | 1   |      |     | 1   | 1   | 1   | 1   | . ( | ) 3 | 3   | 2   | 5     | 4 | 7 | 6 | ( | )   |   |   |     | 1     | 1    |     | 1 | 1 |

| 010      |     | 1   |     |      | 1   | 1.1 | 10. |     | 010 |     | 1   |     |      | 1   | 1   | 1   |     | 2   | 2 3 | 3 ( | 0   | 1   | 6     | 7 | 4 | 5 | ( | )   |   |   |     | 1     | 1    |     | 1 | 1 |

| 011      |     | 0   | .0. | .00  |     |     | 10. |     | 011 |     | 1   | 1   | 1    |     |     | 1   |     | 3   | 3 2 | 2 : | 1   | 0   | 7     | 6 | 5 | 4 | 1 | 1   | 1 | 1 | 1   |       |      | 1   |   |   |

| 100      |     | 1   |     |      | 0   | 0.1 | 01. |     | 100 |     | 1   |     |      | 1   | 1   | 1   |     | 4   | 1 5 | 5 6 | 6   | 7   | 0     | 1 | 2 | 3 | 1 | 1   | 1 | 1 | 1   |       |      | 1   |   |   |

| 101      |     | 0   | .1. | .10  |     |     | 01. |     | 101 |     | 1   | 1   | 1    |     |     | 1   |     | 5   | , 4 | 1 7 | 7   | 6   | 1     | 0 | 3 | 2 | ( | )   |   |   |     | 1     | 1    |     | 1 | 1 |

| 110      |     |     |     | .01  | 0   |     | 00. | 001 | 110 |     |     |     | 1    | 1   |     | 1   | 1   | 6   | 5 7 | 7 4 | 4   | 5   | 2     | 3 | 0 | 1 | 1 | 1   | 1 | 1 | 1   |       |      | 1   |   |   |

| 111      |     |     | .0. |      |     | 0.0 | 00  | 000 | 111 |     |     | 1   |      |     | 1   | 1   | 1   | 7   | ' 6 |     | 5 , | 4   | 3     | 2 | 1 | 0 | 1 |     |   | 1 | 1   |       |      | 1   |   |   |

Figure 10. Build fault testing map for two circuits treated as elements

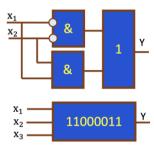

The formula for constructing a fault testing map from a deductive matrix: each 1-coordinate of the deductive matrix is determined by the inverse values of the coordinates of the test (left) set for all 1coordinates of the (upper) vector of the fault table. The obtained vector of the faults to be tested in place of the unit coordinates of the deductive matrix is determined by the alphabet (0,1, "."), where the third character indicates the absence of a fault check at this input coordinate. Each unit coordinate of the deductive matrix denotes the meeting point of the test set with the fault vector, which forms, at this point, the vector of input faults checked on the test set. Thus, the test-fault card solves the issues of fault simulation, fault diagnosis, and test generation for logical functionality of any complexity without processing. Given that any process or phenomenon can be easily digitized and turned into a logical function, this map can serve as a tool for identifying errors in a business process, a social process, or a critical process, including transport, nuclear energy, astronautics, and urban infrastructure. Figure 11 shows the symmetrical circuit and its representation as a function. The synthesis of the fault testing map in Figure 12 of the functionality specified by the logical vector 11000011. The deductive D-matrix is a genome for solving all problems of testing digital functional elements of any complexity. The formula for obtaining a D-matrix is  $D=(L\oplus L_i)_H$ . D-matrix functions are fault simulation on test sets F=D(T) and definition of test sets for fault detection T=D(F). These two functions are explicitly shown on the fault testing map.

The formula for the synthesis of the D-matrix: a quadratic A-matrix of activity is constructed from the logical L-vector of functionality, where each line is a logical vector or its or an inversion  $A_i = L \oplus L_i$  depending on the state of the i-cell of the L-vector, then all the coordinates of the resulting matrix are ordered according to the indices of the quadratic H-matrix (secret key) of bit recoding to obtain a deductive D-matrix, which is a reversible converter of the test set into testable faults and vice versa, where the unit values of the coordinates of the D-matrix build a functional correspondence between the truth table test sets and the faults being tested fault truth table. This fault simulation mechanism has no global analogs regarding manufacturability and efficiency. H-matrix bit recording brings the unordered bits of the A-matrix activity to the standard order of the addresses of the D-matrix rows and columns defined by the binary addresses of the test and fault truth tables.

Figure 11. Structural and functional circuits with symmetry

|     | Test-map                    | D-matrix                        | H-matrix        | Logic vector |

|-----|-----------------------------|---------------------------------|-----------------|--------------|

| 000 | 001 010 011 100 101 110 111 | 000 001 010 011 100 101 110 111 |                 | 11000011     |

| 000 | .111 1 1.1                  | 000 1 1 1 1                     | 0 1 2 3 4 5 6 7 | 1 1111       |

| 001 | .110 1 1.0                  | 001 1 1 1 1                     | 10325476        | 1 1111       |

| 010 | .001 1 1.1                  | 010 1 1 1 1                     | 2 3 0 1 6 7 4 5 | 0 1 1 1 1    |

| 011 | .000 1 1.0                  | 011 1 1 1 1                     | 3 2 1 0 7 6 5 4 | 0 1 1 1 1    |

| 100 | .111 0 0.1                  | 100 1 1 1 1                     | 4 5 6 7 0 1 2 3 | 0 1 1 1 1    |

| 101 | .110 0 0.0                  | 101 1 1 1 1                     | 5 4 7 6 1 0 3 2 | 0 1 1 1 1    |

| 110 | .001 0 0.1                  | 110 1 1 1                       | 67452301        | 1 1111       |

| 111 | .000 0 0.0                  | 111 1 1 1 1                     | 76543210        | 1 1111       |

Figure 12. Fault testing map synthesis for symmetric logical functionality

The superposition of the D-matrix and the two truth tables (test and fault) creates a test-set and fault-set coordinate system (T, F) for all 1-units of the D-matrix. The test map synthesis formula is determined by the superposition of a pair of coordinates for each 1-unit cell of the D-matrix to determine the 1-coordinates of the fault-set with the inverse values of the corresponding bits of the test-set according to the simple rule: If  $F_i = 1$ , then  $D_i = \overline{T_1}$ . The truth table of this analytical coordinate converter (T, L) to F is shown in Table 2.

Table 2. Identifying input line faults

| $T_{i}$ | $L_{i}$ | $F_{i}$ |

|---------|---------|---------|

| 0       | 0       |         |

| 0       | 1       |         |

| 1       | 0       | 1       |

| 1       | 1       | 0       |

Similarly, you can create an alternative test map by placing test vectors on the unit coordinates of the D-matrix, which will detect faults defined in the fault truth table. Thus, it can be argued that the D-matrix is the genome for solving all the problems of functional testing. The matrix's unit coordinates indicate critical functionality areas that test benches must detect. It can be argued that the fault truth table of functionality is a universal source form from which all kinds of faults and functional coverage are extracted. A test is built for malfunctions if the goal is to determine the location, cause, and types of defects in the circuit or model. The functional coverage test aims to verify the functionality defined in the specification. There may be errors in the synthesis stages when one functionality is synthesized. To do this, it is enough to introduce fault into one bit of the logical vector. Detection of such faults is possible only on an exhaustive or complete test. A compromise or cheaper option can be a test to cover the critical points of functionality determined by 1-values of the coordinates of the deductive matrix. Automatic test-bench synthesis can substantially reduce the time-to-market of a digital product with valid Yield parameters.

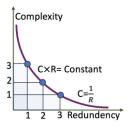

The computational complexity of algorithms multiplied by the redundancy of data structures is a constant value  $C \times R = Constant$  in Figure 13 for solving equivalent problems. Using this rule to synthesize the fault simulation mechanism made it possible to reduce the algorithm's computational complexity to three operations on smart and explicit data structures due to their high level of redundancy. At the same time, the fault simulation process is reduced to zero operations, thanks to the superposition of smart data compiled from two truth tables and one deductive matrix. The simplest implementation of vector-logical fault as address simulation starts with functionality with a single variable as shown in Figure 14. Based on the logical vector, a deductive matrix and a map of tests and repairs are constructed (00, 01, 10, 11).

Figure 13. The relationship between complexity and redundancy

Figure 14. Synthesis of a test map for logical functions of a single variable

The following are the results of a Python application designed to verify data structures and fault modeling algorithms. The fault testing map of the most common functions of two variables in Figure 15 given by logical vectors is presented:  $0111 - L = x_1 \vee x_2$ ,  $0001 - L = x_1 x_2$ ,  $1011 - L = x_1 \vee x_2$ ,  $1101 - \bar{x}_1 \vee x_2$ ,  $1101 - L = \bar{x}_1 \times x_2 \vee x_1 \times x_2$ ,  $1101 - L = \bar{x}_1 \times x_2 \vee x_1 \times x_2$ ,  $1101 - L = \bar{x}_1 \times x_2 \vee x_1 \times x_2$ . The primary purpose of a fault testing map is to simulate (stuck-at and multiple) faults without simulation on input test sets. The H-matrix is the key for fast synthesis of the deductive matrix and fault testing map. The H-matrix is the same for all logical functionalities from n variables. A synthesis of maps for testing the essential logical functions of two variables is presented. This information can be helpful for engineers and students who wish to master the mechanisms of fault simulation, as the truth table addresses. Having learned this lesson, a specialist can manually build a test map for any functionality. Alternatively, a test map synthesis program can be created in a few hours, where the input data is a logical vector, and that is it.

| TT 00 01 10 11 TT 00 01 10 11  00                                                                                                                                                                                                                                                                                                                                                                                       |                                                                | Te       | st-m                                                                                                                                                                                            | ар                                                             |          |                                        |                                                    | D-       | mat                                                        | rix                                                                            |        |                                      | H-m                                                  | atrix                                                                 |                                      |                                                          | A-                           | mar               | tix                                                  |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------|----------------------------------------|----------------------------------------------------|----------|------------------------------------------------------------|--------------------------------------------------------------------------------|--------|--------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|------------------------------|-------------------|------------------------------------------------------|-----------|

| O1                                                                                                                                                                                                                                                                                                                                                                                                                      | TT                                                             | 00       | 01                                                                                                                                                                                              | 10                                                             | 11       | 1                                      | П                                                  | 00       | 01                                                         | 10                                                                             | 11     |                                      |                                                      |                                                                       |                                      | L                                                        | 0                            | 1                 | 1                                                    | 1         |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                      | 00                                                             |          | .1                                                                                                                                                                                              | 1.                                                             | 11       | C                                      | 00                                                 |          | 1                                                          | 1                                                                              | 1      | 0                                    | 1                                                    | 2                                                                     | 3                                    | 0                                                        |                              | 1                 | 1                                                    | 1         |

| Test-map                                                                                                                                                                                                                                                                                                                                                                                                                | 01                                                             |          | .0                                                                                                                                                                                              |                                                                |          | C                                      | )1                                                 |          | 1                                                          |                                                                                |        | 1                                    | 0                                                    | 3                                                                     | 2                                    | 1                                                        | 1                            |                   |                                                      |           |

| Test-map                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                             |          |                                                                                                                                                                                                 | 0.                                                             |          | 1                                      | LO                                                 |          |                                                            | 1                                                                              |        | 2                                    | 3                                                    | 0                                                                     | 1                                    | 1                                                        | 1                            |                   |                                                      |           |

| TT 00 01 10 11 TT 00 01 10 11  00                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                             |          |                                                                                                                                                                                                 |                                                                | 00       | 1                                      | 11                                                 |          |                                                            |                                                                                | 1      | 3                                    | 2                                                    | 1                                                                     | 0                                    | 1                                                        | 1                            |                   |                                                      |           |

| TT 00 01 10 11 TT 00 01 10 11  00                                                                                                                                                                                                                                                                                                                                                                                       |                                                                | Te       | st-m                                                                                                                                                                                            | an                                                             |          |                                        |                                                    | D-       | mat                                                        | rix                                                                            |        |                                      | H-m                                                  | atrix                                                                 |                                      |                                                          | Δ-                           | mar               | tix                                                  |           |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                      | TT                                                             |          |                                                                                                                                                                                                 |                                                                | 11       | 1                                      | П                                                  |          |                                                            |                                                                                | 11     |                                      |                                                      | 46117                                                                 |                                      | L                                                        |                              |                   |                                                      | 1         |

| 01                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |          | -                                                                                                                                                                                               |                                                                |          |                                        |                                                    | -        | -                                                          |                                                                                |        | 0                                    | 1                                                    | 2                                                                     | 3                                    | _                                                        |                              |                   |                                                      | _         |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |          |                                                                                                                                                                                                 | 1.                                                             |          |                                        | -                                                  |          |                                                            | 1                                                                              |        | -                                    | _                                                    | _                                                                     | _                                    | -                                                        |                              |                   |                                                      |           |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |          | .1                                                                                                                                                                                              |                                                                |          |                                        |                                                    |          | 1                                                          |                                                                                |        | 2                                    | 3                                                    |                                                                       |                                      |                                                          |                              |                   |                                                      |           |

| Test-map                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |          |                                                                                                                                                                                                 | 0.                                                             | 00       |                                        |                                                    |          |                                                            | 1                                                                              | 1      | _                                    | 2                                                    | -                                                                     |                                      | -                                                        | 1                            | 1                 | 1                                                    |           |

| TT 00 01 10 11 TT 00 01 10 11  00                                                                                                                                                                                                                                                                                                                                                                                       |                                                                | -        |                                                                                                                                                                                                 |                                                                |          |                                        |                                                    | _        |                                                            |                                                                                |        |                                      |                                                      |                                                                       |                                      |                                                          |                              |                   |                                                      |           |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                      | **                                                             |          |                                                                                                                                                                                                 |                                                                |          |                                        | _                                                  |          |                                                            |                                                                                |        |                                      | H-m                                                  | atrix                                                                 |                                      |                                                          |                              |                   |                                                      |           |

| O1                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                | 00       |                                                                                                                                                                                                 | 10                                                             | 11       |                                        |                                                    | 00       |                                                            | 10                                                                             | 11     | •                                    |                                                      | •                                                                     | 2                                    | _                                                        | 1                            | -                 | 1                                                    | 1         |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |          |                                                                                                                                                                                                 |                                                                |          | _                                      | -                                                  |          |                                                            |                                                                                |        | -                                    | _                                                    | _                                                                     | -                                    | _                                                        |                              | 1                 |                                                      |           |

| Test-map                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |          | .0                                                                                                                                                                                              | 1.                                                             |          |                                        |                                                    |          | 1                                                          | 1                                                                              | _      | _                                    | -                                                    | -                                                                     |                                      | -                                                        | 1                            |                   | 1                                                    | 1         |

| Test-map                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |          |                                                                                                                                                                                                 |                                                                | 01       |                                        |                                                    |          |                                                            |                                                                                | 1      |                                      | -                                                    | -                                                                     |                                      |                                                          |                              |                   |                                                      |           |

| TT 00 01 10 11 TT 00 01 10 11                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                             |          |                                                                                                                                                                                                 | 0.                                                             |          | 1                                      | 11                                                 |          |                                                            | 1                                                                              |        | 3                                    | 2                                                    | 1                                                                     | 0                                    | 1                                                        |                              | 1                 |                                                      |           |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                | To       | st-m                                                                                                                                                                                            | ap                                                             |          |                                        |                                                    | D-       | mat                                                        | rix                                                                            |        |                                      | H-m                                                  | atrix                                                                 |                                      |                                                          | Δ-                           | mar               | tiv                                                  |           |

| 01                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                | 16       |                                                                                                                                                                                                 |                                                                |          |                                        |                                                    |          | mac                                                        |                                                                                |        |                                      |                                                      |                                                                       |                                      |                                                          |                              | IIIai             | LIA                                                  |           |